)

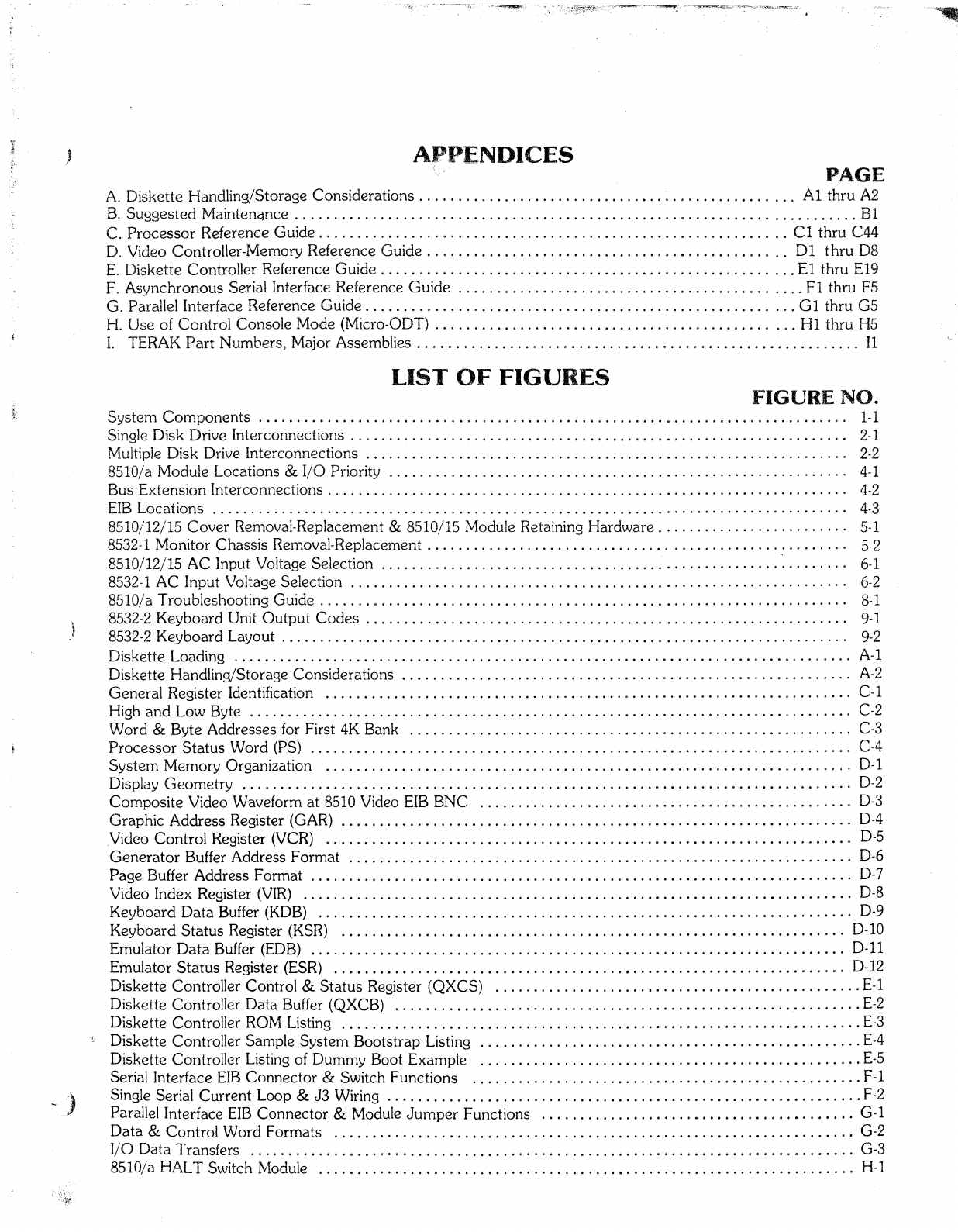

APPENDICES

PAGE

A.

Diskette Handling/Storage

Considerations.

. . .

.. ..

~

..

1 1

••••••••••••••

1

•••••

~

••••••••••

, • •

••

Al

thru

A2

B.

Suggested Maintenance 0 • 0

••••••••••••••

0

••••••

>

•••

0'

••••••••••

0 • 0

••

0 • 0

••••••

0 0 • 1

010

•••••

BI

C. Processor Reference Guide 0

•••

0.0

•••••••

1'

•••

1

••••••••••

1

•••

1

•••

1

••••••

0

•••••••••

0

......

Cl

thru

C44

D. Video Controller-Memory Reference Guide

...

0'

•••••••••••••

0

••••••

0

•••••••

0

••••

0 1 0

•••

0

'0

Dl

thru

08

E.

Diskette Controller Reference Guide

..

0

•••••••••••••

0 • o

••••••••••••

o

••

o0

El

thru

E19

F.

Asynchronous

SeriaI Interface Reference

Guide

1'

•••••••••••••••••••

0

••••••••

0 0

••••••

fl

thru

F5

G. Parallel Interface Reference Guide

~

Gl

thru G5

H.

Use

of

Control

Console Mode (Micro-OOT) 1

•••••

1

••••••••••••••••

1

•••••

~

•••••••

••

•

••

Hl

thru

1-I5

1.

TERAK

Part

Numbers, Major Assemblies 1

•••••••••••••••••••••••••••••••

0

,"'

••••

1,.1.

Il

LIST

OF

FIGURES

FIGURE

NO.

System Components '0 • 1

••

0

•••••

0 • 0

••••

0 0

••

1··1

Single Disk Drive Interconnections 0

••

0

•••

0 • 0

••••••

0 • 0 • 0

••

0

••••

0

•••

0 0 0

••

0

•••

0 0 0 • 0 • 0

••••

0

•••

0 • 0

2-1

Multiple Disk Drive Interconnections o

••

0

••••••

0 • 0

•••••••

0

•••••••••••••

000

••

0 • 0 • 0

••

0 0

•••••

0 • " 0

••••

0 0

2-2

8510/a Module Locations &

I/C)

Priority

0.0

•••••••••

0

••••••

0.

0 • 0

••

0

•••

0 0

••••

0 • 0

••••••••

0

••

0

••

'0'

0 •

••

4-1

Bus Extension Interconnections 0

•••••

0

••

0

•••

0 • 0 • 0

••••

0

•••

0

•••••••

0 0 • 0 • 0 • 0

••

0 • 0

•••••••

0 • 0 0

••

0 • • • • •

••

4-2

EIB

Locations

..

0

••••

0

•••••

0 0 • 0

•••••

0

•••••••••

0

•••••

0

••••

0 • 0 • 0 • 0 • 0

••

0

•••

0 0

••

0 0 0 0

••••

0 • 0

•••••••••

0

4-3

8510/12/15

Caver

Removal-Replacement &8510/15 Module Retaining Hardware 0

00

••••

0

•••

0

••

0 •

0.01.

• •

••

5-1

8532-1

Monitor Chassis Ren1oval-Repla.cement 0 0 • 0 0

•••••••

0 0

••••

0

••

0

••

0

••

0 0 • 0

•••••••••••

0 • • •

••

• 0 • •

••

5-2

8510/12/15 AC Input Voltage Selection .000

•••••••

0

•••••

0

•••••

'0

••

0 • 0 • 0

••

0.

0

.0'

••••

0 0

••

0

•••

'~

•

••••

•

••

6-1

8532-1

AC Input Voltage Selection

..

0

•••

0

•••••

0

••••••••••••••••

0 • 0

•••

0

••••••••

0 0 • 0

••••

0

••••••••

0

••

0

6-2

8510/a Troubleshooting Guide

000

•••

0

•••

0

••

0.0

•••••

000.0

•••••••••••

0

••••••

0 •

••

8-1

8532-2

Keyboard Unit Output Codes

00

••

0.00.0

••

0

•••••

0 0

•••

0

•••

0

••••••••

0

•••••••

0 0 •

00'

•••••

0

•••

0 •

••

9-1

8532-2

Keyboard

Layout .0 • 0 • 0

•••••

0 0 • 0 0 0

•••

0

••

0 • ,

•••

0

••••••••••••••••••

0

••••••

0 • 0

••

0 • 0 0 •

000

..

0 • • •

••

9-2

Diskette Loading

..

0000

•••

0 0 • 0 0 • 0

.0'

•••

0 • 0 0

•••••••••••••••••

0 • 0

•••

0

••

0

••••

0'

•••••••

00.

00

••••••••••

A-l

Diskette HandlingJStorage Considerations

...

0

••••

0 • 0

••

0

••••••••••

0

••

0

•••••••••••

0

••

0

••

0

••••

0 0 • • • • •

••

A-2

General I<egister Identification 0 0

•••

0 0 0 • 0 • 0

••

0 • 0 0 • 0

••

0 • 0 • 0 0

••••

0 0 • 0 0 0

•••

0000000• 000

••

0 0

•••

0

•••

0 • 0 •

o'

C-l

High and Law Byte .0 0 0 0

••

0

••

0

••

0 • 0 0 0 0 0

••

0 • 0 •

0"

••

0

••

0 • 0 0

••••

0 • 0 • 0 • 0 0 0 0 • 0 0

•••••••••••

0 •

'.

0

••••••••

0 0

C-2

Ward

&Byte Addresses

for

First

4K

Bank

o,.

0 • 0 • 0

•••

0

••

0 • 0

•••

0 0 • 0

••••

0 0 • 0

••••

0 • 0 • 0

•••

0 0 0 • 0 • 0

•••

0 •

••

C-3

Processor Status Ward (PS) o

••

0

••••••••

0 0 • 0 • 0 0

••••••

0

•••••••

0

••••

0 • 0 0 • 0 0

••

0 • 0 0

•••

0

••

0

••

0 • 0 0 • 0

•••

0 0 C-4

System Memory Organization .0 • 0

••••••

0 0

•••••••

0 • 0

•••••••••

0 0

•••••••••••••

0 0

•••••

0 • 0

••••

0 0

••

0 • •

••

D-1

Display Geometry

..

0

••

0 • 0

••••••••

0

•••••••••

0 0

••

0

••••••••••••

0

••••••••••••

0 0

••

0

•••••

0 • 0 0 • 0

••••••••

'D-2

Composite Video Waveform at 8510 Video

EIB

BNe

0

•••••••

0 •

o'

•0

••••••

0 • 0 • 0 0

•••••••••

00

D-3

Graphie Address Register (GAR) 0 0

•••

0

•••

0 • 0

••

0

•••••••

0

••••••

0

••

0

•••••

0 • 0

•••••

0

•••

0

••

0

••

0 0 0

•••

0

••

0 0

D-4

,Video Control Register (VeR)

..

0

•••

0 • 0 •

00'

••

0

••

0 0

•••••••••••

000

•••

0 0 • 0 • 0

••

0 • 0 • 0 0

00

••

0

•••

00'

00'

0 0

.0

D-5

Generator Buffer Address Format

o.,

0 0 0 0 0 0 0

••

0 0

••

0 • 0 • 0

•••

00'

0

•••

00

••

0

00'

••••••

0

.00.

0 • 0 • 0

0000

•••

0 •

o'

0-6

Page Buffer Address

Format.

0 0 • 0 • o

••

0 • 0 • 0 0 • 0 • 0 • 0 0 0 • 0 0 0

••

0

••

0

0000000

••

00'

0 0

0000

••

0 0 0

0000000

••••••

o'

D-7

Video Index Register

(VIR)

0 0

••••

0 • 0 0 0

••

0 0 0 0 • 0 0

••

0

••

0 0

•••

0

•••

0 0 0 0

••

0 • 0 0 0 0 0 • 0

••

0 0 • 0 • 0 0 0 0 0 0 0

••••

0

••

0 0

D-8

Keybaard Data Bufter

(KDB)

0 0 0

••

0 • 0 0 0 0 • 0 0

•••••••

0 0

••

0 0

••••••

0

••

0 0

••

0 0 • 0 • 0 0 0

••••

0 0 • 0

••

0 0

••

0

D-9

Keyboard Status Register

(KSR)

.0 0

••

0 0 • 0 0 0 • 0

••••••

0 0 0

••••

0

•••••••••••

0

•••

0000• 00000

••

0 0 0 0 0 0

••••

o'

0-10

Emulator Data Buffer

(EDB)

o'

0

••

0 0 • 0 0

••

0 0 0

••••••

0

•••••••

0

••

0 0 • 0 • 0 0

••••

0 0 • 0 0 0 • 0 • 0 0 0 0 • 0 0 0 0 0 • 0

D-11

Emulator Status Register

(ESR)

...

0 0 0

••

0 • 0 • 0 0

••

0 0

•••

0 0 0 0 • 0 0 • 0 0 • 0

••

0

••••

0 0 • 0 0 0

•••

0

••

0 0 • 0 • 0 0 0 0 0

••

0 • 0

0-12

Diskette Controller Control &Status Register (QXCS)

00'

o'

0 0

•••

0 • o

••••

0

••

0'

00'

••

00000

•••

000

•••••

o.

00'

E-l

Diskette Controller Data Buffer (QXCB)

..

0.0

•••

0 0

•••

0 • 0

•••••••••••••••••

0 • 0

••

0

••••

0

•••

0'

0 •

00

• 0

.0

••••

E-2

Diskette Controller

ROM

Listing 0 0 • 0 0 • 0 0 0

••

0 0 • 0 0

•••••••••••••

0 0

•••••••••

0 • 0 0 0

••

0 0

••••••

0 0 0

••••••••

0 •

E-3

Diskette Controller Sample System Bootstrap Listing o

••

0

•••

0 0

••••••

0 0

•••

0 0 0 0 • 0 • 0

••••

0

•••

0 0 0 0

...

0 0

••••••

E-4

Diskette Controller Listing of Dummy Boat Example

....

0

••

0

•••••••••••

0 0 0

•••••••

0 0 0 0

••

0 0 0

•••

0

••••

0 • 0 •

E-5

SeriaI Interface

EIB

Connector &Switch Functions o

•••••••

000

••

00'

••

00'

0.00000.

0

o'

••

0

••

0.0

••

0

••

o'

•••

F-1

Single Seriai Current Loop &J3 'Wiring

..

0 0

••

0 0

•••

0 0

000

••••

0 • 0 •

o'

00'

0000

••••

0

••

0

•••

0 0 • 0 0 • 0

.00000.00

••

F-2

Parallel Interface

EIB

Connector &Module

Jumper

Functions

.0.0

••

0 • 0

•••

0 • 0

•••

0 •

0000000.

0

••

o'

•0000000 G-1

Data &Control Word Formats 0 0 • 0 0 • 0

••••

0

•••

0 0

••••••••••••

0 • 0 0

•••••

0

••

0

•••

0 • 0 • 0

•••••

0

••

000

••

0 • 0 • 0

G-2

1/0 Data Transfers

.0

•••••••

0

•••••

0

••

0

••

0

000

••••

0 0 0 • 0

•••••

0

••

0 • o

••••

00

••

0

••••

0 0

••

0 • 0

•••

0

••

0 •

00

••

o'

G-3

8510/a HALT Switch Module

...

0 0

•••••

0 0

••••••••

0

••••

o'

•••••

0

•••••

0

0.0

••••

0

••••••••

0 0

••

00'

••

0 0

••••

H-1