Epiq Solutions Proprietary

Revision History

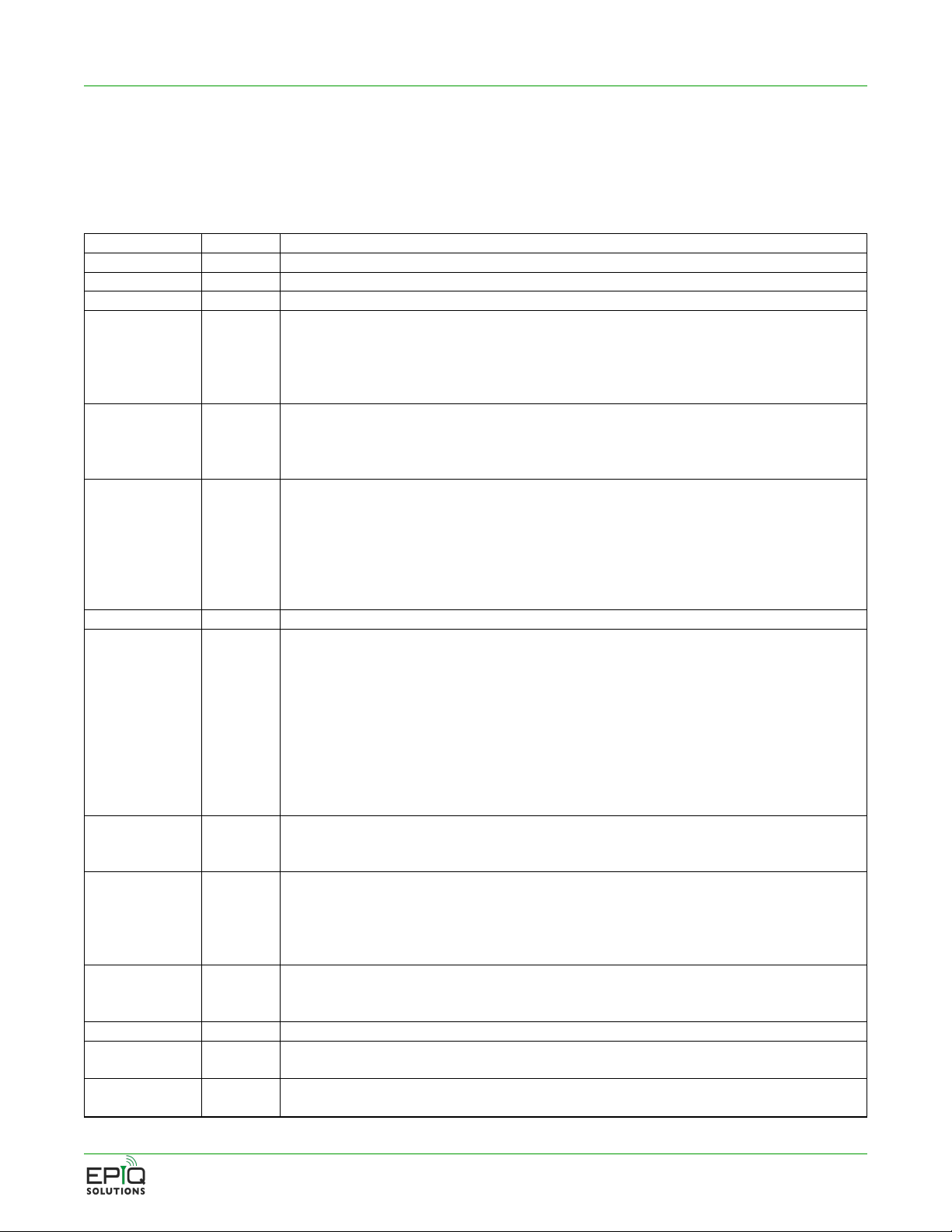

Date Version Description

09/27/2017 3.7 Initial Release

02/28/2018 3.8.1 Update instructions for configuring FPGA and other minor updates

06/07/2018 3.9.0 Clarification on versioning

08/23/2018 3.10.0 Add support for external GPS module.

Fix user_app timing constraints. Add support for Reference DAC SPI. Add iq multi-

pliers.

Move location of golden image.

First X4 release.

10/11/2018 3.10.1 Document change, Section 8.3, change -c 1 to -c 0

Fix Tx Late timestamp getting stuck where the data_rd_counter reset is not syn-

chronized to the Tx clock domain causing metastability and incorrect reset state for

data_rd_counter once the reset pulse goes low.

01/05/2019 3.11.0 PCIe ip block now has its boundary at the core_wrapper.

Add timing optimization looping to the build script.

Add manual trigger.

X2, added 245.76 Mhz ObsRx.

X4, added dual two channel phase coherent and four channel independent Rx modes.

Added single channel on dual JESD lane for ObsRx in anticipation of 491.52 MHz

ObsRx.

02/22/2019 3.11.1 X4, update timing constraints to support 250 Mhz

06/25/2019 3.12.0 Add supoort for high sample rate Tx where dual JESD lanes are required for a single

channel. Modified high speed ObsRx on X2 such that get two samples for clock.

Add decimator on channels Rx1/Rx2. For X4, all Rx sample clocks are now driven

from the same Rx clock source, all ObsRx sample clocks are now driven from the

same ObsRx clock source, and all Tx sample clocks are now driven from the same Tx

clock source.

Fix PCIe Tx when packet size is larger than FIFO size. Add frequency hopping control

logic.

Upgrade to Vivado 2017.4 from 2016.4.

Add iq swap mode. Added JESD Tx sample data memories to user_app.

10/04/2019 3.12.1 Minor changes to improve JESD synchronization.

Doubled the PCIe Rx FIFO size on X4 ObsRx ports to support 491.52 MHz sample

rates so that the Rx FIFO does not go full.

12/6/2019 3.13.0 Add support for User App GPIO control and user app RFIC SPI interface.

Add user_pdk_config.v parameter file.

X4 Only, Add support for transmitting via PCIe on Tx channels A1 and B1.

Add WBSTAR 100 ms delay when reconfiuring the FPGA via ICAPE.

X4 Only, Double the Rx FIFO size to help with timestamp gaps at higher sample rates.

6/05/2020 3.13.1 X4 Only, Updates for RevC board testability.

X4 Only, Increase Rx and ObsRx FIFO depths.

X2 Only, update Rx packet header to v1.

8/02/2020 3.14.0 Fix dual Tx underrun reporting bug.

01/14/2021 3.14.1 Upgrade to 8 lane PCIe for HTG-K800 and HTG-K810.

Fix for starting/stopping streaming on a 1PPS edge.

04/06/2021 3.15.0 Fix Tx Timestamp dropped packets after late bug.

Fix JESD Tx bug.

continues on next page

©2023 Epiq Solutions, All Rights Reserved v